SHIFT REGISTERS

- 1. D.SHUNMUGA KUMARI ASSISTANT PROFESSOR DEPARTMENT OF INFORMATION TECHNOLOGY SHIFT REGISTERS

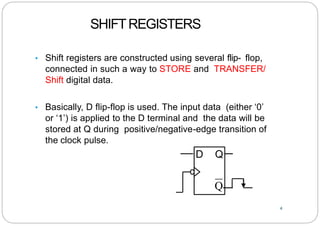

- 2. SHIFTREGISTERS • Shift registers are constructed using several flip- flop, connected in such a way to STORE and TRANSFER/ Shift digital data. • Basically, D flip-flop is used. The input data (either ‘0’ or ‘1’) is applied to the D terminal and the data will be stored at Q during positive/negative-edge transition of the clock pulse. 4 D Q Q

- 3. 5 • One D FF is used to store 1-bit of data. Thus, the number of flip-flops used is the same with the number of bit stored. • Shift register mean that the data in each FF can be transferred/move to other FF upon edge triggering of the clock signal. Four types of data movement in shift register are:- • SISO-Serial In Serial Out • SIPO- Serial In Parallel Out • PISO-Parallel In Serial Out • PIPO-Parallel In Parallel Out SHIFTREGISTERS

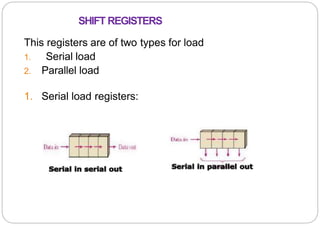

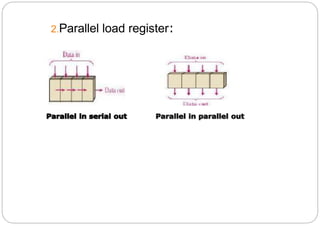

- 4. This registers are of two types for load 1. Serial load 2. Parallel load 1. Serial load registers: SHIFT REGISTERS

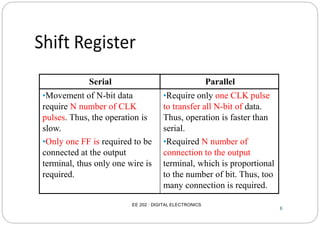

- 6. 6 Serial Parallel •Movement of N-bit data require N number of CLK pulses. Thus, the operation is slow. •Only one FF is required to be connected at the output terminal, thus only one wire is required. •Require only one CLK pulse to transfer all N-bit of data. Thus, operation is faster than serial. •Required N number of connection to the output terminal, which is proportional to the number of bit. Thus, too many connection is required. EE 202 : DIGITAL ELECTRONICS

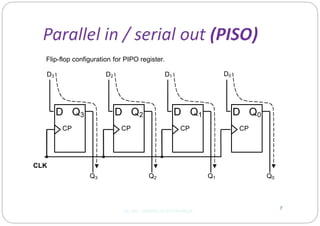

- 7. 7 D Q2 CP D Q1 CP D Q3 CP D Q0 CP D0 Q3 Q2 Q1 Q0 Flip-flop configuration for PIPO register. D3 D2 D1 CLK EE 202 : DIGITAL ELECTRONICS

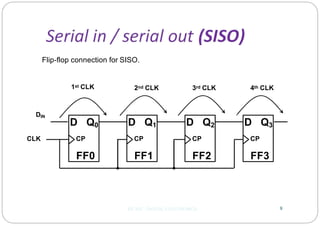

- 8. 9 Flip-flop connection for SISO. FF1 D Q1 CP FF2 D Q2 CP FF0 D Q0 CP FF3 D Q3 CPCLK DIN 1st CLK 2nd CLK 3rd CLK 4th CLK EE 202 : DIGITAL ELECTRONICS

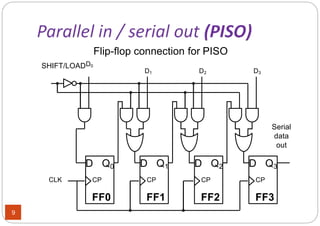

- 9. Flip-flop connection for PISO 9 FF1 D Q1 CP FF2 D Q2 CP FF0 D Q0 CP FF3 D Q3 CPCLK D1 D2 D3 SHIFT/LOADD0 Serial data out

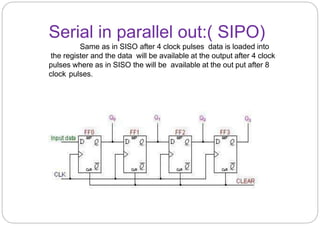

- 10. Serial in parallel out:( SIPO) Same as in SISO after 4 clock pulses data is loaded into the register and the data will be available at the output after 4 clock pulses where as in SISO the will be available at the out put after 8 clock pulses.

- 11. APPLICATION S • Pseudo random pattern generator • Ring counter • Johnson counter or twisted counter